# デジタルコヒーレント光通信用波長可変レーザ制御IC

五十川 知 子\*•田 中 啓 二·坂 野 英 一 金 子 俊 光·上 坂 勝 己

Tunable Laser Controller IC for Coherent Optical Communication Systems — by Tomoko Ikagawa, Keiji Tanaka, Eiichi Banno, Toshimitsu Kaneko and Katsumi Uesaka — The authors have successfully developed a tunable laser controller IC for digital coherent optical communication systems. The developed IC is composed of both analog and digital circuits fabricated by CMOS (Complementary Metal Oxide Semiconductor) process, which contributes to the reduction of chip size and power dissipation. The IC, used in combination with in-house tunable laser module, achieves even lower power dissipation by introducing switching regulators and can be implemented to small tunable assemblies such as micro-ITLA (Integrable Tunable Laser Assembly). This paper outlines the development of the tunable laser controller IC and its performance when used with the in-house tunable laser module.

Keywords: tunable laser, coherent, integrated circuit

### 1. 緒 言

近年の通信トラフィックの増大に伴い、光伝送装置の小型化・低消費電力化が求められている。大容量の通信が可能であり、現在導入が進んでいるデジタルコヒーレント光通信システムでは、従来の300pinトランスポンダから小型なプラガブルトランシーバへの移行が検討されており、OIF (the Optical Internetworking Forum)では業界共通仕様に対する議論が進められている。

それに伴い、このシステムに搭載される波長可変光源の小型化・低消費電力化も要求される。現在300pinトランスポンダにはITLA (Integrable Tunable Laser Assembly)<sup>(1)</sup> が搭載されているが、プラガブルトランシーバでは、ITLAよりも小型な micro-ITLA <sup>(2)</sup>、もしくはさらに小型な波長可変光源の搭載が検討されている。

今回、micro-ITLA等の小型波長可変光源に搭載可能な 波長可変レーザ制御ICを開発した。当社製波長可変レーザ に対して最適設計した回路を1チップのICに集積すること で回路の小型化・低消費電力化を図った。本稿では、波長 可変レーザ制御ICの構成と、当社製波長可変レーザと組み 合わせた場合の基本特性について報告する。

#### 2. 主要開発仕様

表1に波長可変光源の主要開発仕様を示す。供給電源電圧については、単一電源に対する要望を想定して3.3Vの単一電源とし、消費電力は3.5W以下とした。また、周波数誤差\*1については、+/-1.5GHz以下、波長切替時間については、時間短縮の要求を想定して50ミリ秒以下に設定した。

表1 波長可変光源の主要開発仕様

| 項目      | 目標              | micro-ITLA(OIF仕様)     |

|---------|-----------------|-----------------------|

| 供給電源電圧  | +3.3V           | +3.3V, -5.2V, +1.8V*1 |

| 消費電力    | 3.5W Max.       | 5.0W Max.             |

| 周波数誤差*1 | +/- 1.5GHz Max. | +/- 2.5GHz Max.       |

| 波長切替時間  | 50 msec Max.    | 10 sec Max.           |

\*1:オプション仕様

#### 3. 波長可変レーザ制御ICの構成

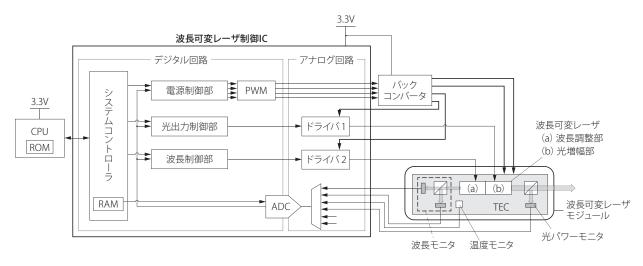

図1に今回開発した波長可変レーザ制御ICを用いた波長可変光源のブロック構成を示す。波長可変光源は、主に波長可変レーザを収納した波長可変レーザモジュール、外部との通信を行なうCPU、波長可変レーザ制御IC、バックコンバータ\*2からなり、CPUとバックコンバータ以外の主要回路は全て波長可変レーザ制御ICに集積されている。

波長可変レーザ制御ICは、CMOSプロセスを用いて設計したアナデジ混載ICであり、主な機能は、①電源制御、②光出力制御、③波長制御、④CPUとのシリアル通信である。主に、波長可変レーザに電流を供給するためのドライバ、波長可変レーザ等のモニタ電圧をデジタル値に変換するADC(Analog to Digital Converter)、3つのデジタル制御部(電源制御部、光出力制御部、波長制御部)、PWM(Pulse width modulation)、システムコントローラを備えている。電源制御部とPWMは、バックコンバータと組み合わせて電力効率の高いスイッチングレギュレータとして機能し、レーザ温度を調整するためのTEC(Thermoelectric cooler)の印加電圧とドライバの電源電圧を生成する。シ

図1 波長可変光源のブロック構成

ステムコントローラは、内部に半自立的制御を行なうためのステートマシン\*3、RAM(Random Access Memory)、CPUとの通信を行なうためのSPIインターフェースを備えており、CPUは100程度の設定波長に対応したレーザ動作条件をルックアップテーブルとして内部のROM(Read Only Memory)に持たせ、要求された設定波長に関する動作条件のみを波長可変レーザ制御ICのRAMに転送するだけで波長可変レーザを自動制御できる構成とした。

以下、本開発における①消費電力低減、②波長可変レーザの 制御、③波長切替時間の短縮に関する構成について紹介する。

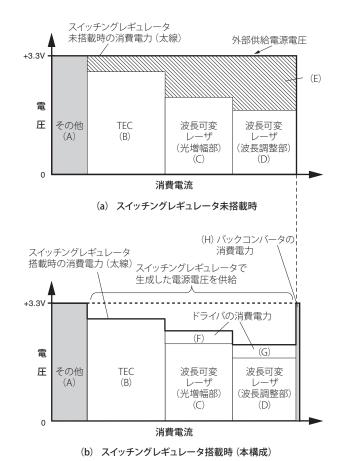

3-1 スイッチングレギュレータによる消費電力低減 波長可変光源の消費電力の大部分は、波長可変レーザと TECの消費電力が占める。図2 (a) に示すように、外部から供給される3.3Vの電源電圧を直接ドライバとTECに使用した場合、消費電力は消費電流と3.3Vの積、つまり太線で囲まれた長方形の領域となる。なお、その他と明記されている部分(A)は、波長可変レーザ制御ICのドライバを除いた箇所の消費電力とCPUの消費電力の合計値である。また、波長可変レーザについては、光増幅部と波長調整部で印加すべき電圧が異なるため(C)と(D)にわけて表示している。TECと波長可変レーザで消費される電力は(B)、(C)および(D)の領域のみであり、斜線で示された(E)の領域はドライバ等の回路で浪費される電力となる。

この不要な消費電力を低減するため、今回開発した波長可変レーザ制御ICでは、電源制御部とPWMを内蔵し、IC外部のバックコンバータと合わせて任意の電源電圧を生成できるスイッチングレギュレータを構成している。図1に示すように、スイッチングレギュレータでは、PWMにて各部に最適な電圧に相当するパルス幅の信号を出力し、バックコンバータでDC電圧に変換することで、各部に電圧を供給する。回路の電圧降下等による電圧変動を補正するため、ADCにてバックコンバータの出力電圧を常に読み出し、電源制御部を用いて負帰還制御することで電圧を一

定に保つ構成にしている。**図2 (b)** に示すように、本構成では、スイッチングレギュレータを用いて高効率に電圧を降圧することで消費電力を太線で囲まれた領域まで低減できる。ドライバについては、ドライバ自体に印加すべき電圧を極力下げる構成に設計することで、ドライバの消費電

図2 波長可変光源の消費電力

力 (F) および (G) を抑える構成をとった。この構成では、バックコンバータの消費電力 (H) が加算されるが、この値はスイッチングレギュレータで低減できる消費電力に比べて小さい。

一般的に、スイッチングレギュレータは電力効率が高い 半面、出力ノイズが大きくなる傾向がある。コヒーレント 光通信システムでは、光の位相を変化させることで信号を 伝送するため、波長可変光源から出力される光のスペクト ル線幅が太くなると信号に対する位相ゆらぎが増大するこ ととなり、伝送特性に大きな影響を与える。そのため、本 開発ではドライバの出力ノイズを非常に小さく抑えること が求められ、そのためにはバックコンバータの出力ノイズ、 およびバックコンバータ出力からドライバ出力へ伝搬する ノイズを抑える構成が必要となる。

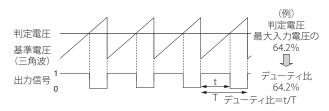

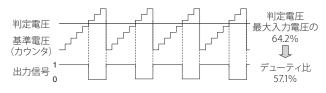

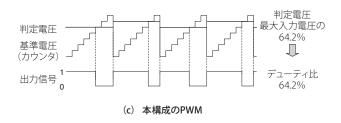

図3(a)に、一般的なアナログ制御によるPWMの波形を示す。この構成では、三角波の基準電圧と判定電圧を比較し、比較結果に応じたパルス幅の信号を生成する。パルス信号は、後段のバックコンバータにおいてパルス信号をそのデューティ比(1周期の間に"1"を出力する時間の割合)に比例したDC電圧に変換する。したがって、出力電圧に対する分解能、つまりデューティ比に対する分解能が低いと電源制御部の負帰還制御における出力電圧変動が大きくなり、また三角波の周波数に相当するスイッチング周

(a) 一般的なアナログ制御によるPWM

(b) 一般的なデジタル制御によるPWM

図3 PWM出力波形

波数が低いとバックコンバータで遮断しきれない低周波の ノイズが大きくなる。

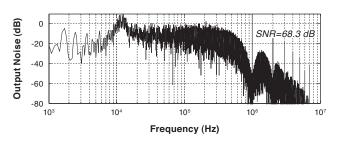

アナログ制御によるPWMでは、デューティ比に対する 分解能が無限であり、スイッチング周波数を十分高く設定 できることから良好な特性が得られる。しかし、本開発で はPWMを4回路搭載する必要があり、アナログPWMで は回路サイズが増大してしまうため搭載できない。一方、 図3(b)に示すような一般的なデジタル制御によるPWM では、スイッチング周波数とデューティ比に対する分解能 の両立が難しい。例えば、1MHzのスイッチング周波数で 16ビットの分解能を得るには65.5GHzの発振器が必要と なり、消費電力の増加を伴う。そこで、今回開発した波長 可変レーザ制御ICでは、デジタル制御によるPWMの構成 に対して、ΣΔ変調回路で変調した信号を判定電圧とする 構成を取り入れた。図3(c)に示すように、本構成では、 ΣΔ変調回路を用いてパルス幅を時間変化させることで デューティ比に対する分解能を高めることができるため、 1MHzのスイッチング周波数に対して3~4ビットのカウ ンタが適用でき、発振器の周波数を消費電力の増加を伴わ ない8~16MHz 程度に設定できる。図4(a)に、本構成に おけるバックコンバータ出力のノイズスペクトルの計算結 果を示す。本構成では、1MHzのスイッチング周波数にお いて16ビットの電圧設定分解能があり、68.3dBのSNR (Signal to Noise Ratio) が得られている。

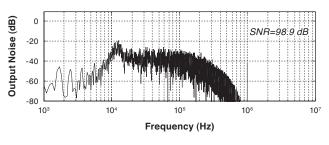

しかし、上記のスイッチングレギュレータ出力に対する ノイズ低減だけではノイズは抑えきれず、バックコンバー タ出力からドライバ出力へ伝搬するノイズを抑える構成が 必要となる。図1に示すように、バックコンバータ出力の

(a) バックコンバータ出力

(b) ドライバ出力

図4 ノイズスペクトル

うち2つはドライバの電源電圧として使われる。本ICでは、電源電圧変動除去比(PSRR: Power Supply Rejection Ratio)の良いドライバを設計することで、スイッチングレギュレータの出力ノイズがドライバ出力に伝搬するノイズを抑えた。図4(b)に、ドライバ出力のノイズスペクトルの計算結果を示す。SNRは98.9dBまで改善できており、外部の安定電源を供給した場合と同程度のノイズ特性が得られる見込みを得た。

3-2 波長可変レーザの制御 図1に示すように、波 長可変レーザモジュールには、波長可変レーザとTECの他 に、光出力をモニタするための光パワーモニタ、波長モニ タ、温度モニタを内蔵している。今回開発した波長可変 レーザ制御ICでは、光パワーモニタ、波長モニタの値を用 いて波長可変レーザの光出力と発振波長を制御する回路を 搭載している。具体的には、光パワーモニタおよび波長モ ニタから出力された電圧をADCにてデジタル値に変換し、 それぞれ光出力制御部、波長制御部にて目標値とのずれを 求め、そのずれを補正するよう演算処理した値をドライバ に入力し、波長可変レーザに供給する電流を制御する。温 度モニタに対しては、ADCでデジタル変換された値を CPUに転送し、CPUを介してTECに対する負帰還制御を 行なうことで、レーザ温度を一定に保つ。本ICでは、これ らの負帰還制御の演算処理をデジタル回路に持たせること で、回路サイズと消費電力の低減を図った。デジタル制御 では演算による精度劣化が懸念されるが、固定小数点演算 における桁数を最適化することで回路サイズを抑えつつ精 度を確保する構成とした。波長制御部については、低雑音 のΣΔ型DAC (Digital to Analog Converter) を搭載した ドライバを用いることで発振波長に対する精度を確保した。

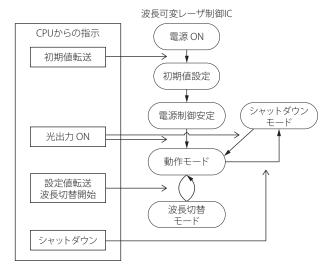

3-3 波長切替時間の短縮 今回開発した波長可変 レーザ制御ICは、システムコントローラに半自立的動作を 行なうステートマシンを備えており、CPUとのSPIイン ターフェースによる通信によって生じる時間的制約を受け ることなく、波長可変レーザを安定制御する構成としてい る。図5にステートマシンの概略を示す。波長可変レーザ 制御ICは外部からの電源電圧供給後、CPUから転送され た初期値を用いて内部回路を設定したのち、電源制御を開 始し、TECとドライバに所望の電圧を供給する。その後、 CPUからのトリガ信号を受けて光出力制御、および波長制 御を開始し、安定動作状態に移行する。波長切替をする際、 CPUは波長可変レーザ制御ICに対して、次の設定波長に 対するパラメータと波長切替を指示するトリガ信号のみを 転送し、波長可変レーザ制御ICはそれらの信号を受けて自 動で波長切替を実行する。この構成により、CPUの負荷を 増大させることなく短時間で波長切替を実行することが可 能である。

また、さらなる波長切替時間の短縮として、負帰還制御の応答速度を速める機能を搭載した。デジタル回路による負帰還制御の時定数は、制御ループにおける係数とADC

図5 ステートマシンの概略

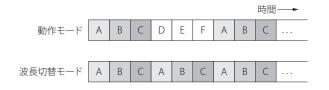

のサンプリング周期によって決まる。図6に示すように、本ICでは、波長可変レーザの動作が安定している時には、A~Fの全ての項目をモニタし、設定波長の切替時にはA~Cの光出力および発振波長に関わる項目のみ値をモニタすることで、切替時間を短縮する構成を持たせた。

図6 ADCのデータ取得のタイミング構成

#### 4. 諸特性

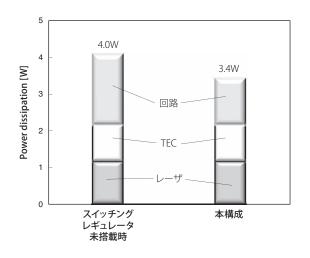

図7に、開発した波長可変レーザ制御ICを用いて当社製波長可変レーザを制御した際の消費電力の測定結果を示す。スイッチングレギュレータ未搭載の構成では、消費電力は4.0Wであり、目標の3.5Wに到達しない。一方、本構成における消費電力は3.4Wであり、スイッチングレギュレータによる消費電力低減の効果によって目標値を満足した結果が得られている。

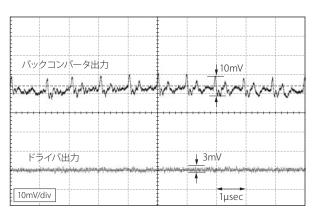

図8に、バックコンバータとドライバの出力波形を示す。バックコンバータ出力では、出力ノイズが10mV程度に抑えられている。一方、ドライバについては、出力ノイズは3mV程度の変動に収まっており、バックコンバータの出力ノイズとの相関が見られていないことから、バックグラウンドノイズもしくはドライバ自体のノイズが支配的になっていると考えられる。電源電圧変動除去比の良いドライバ

図7 消費電力の測定結果

図8 出力波形

を設計したことで、スイッチングレギュレータの出力ノイズが波長可変レーザに与える影響を低減できており、外部供給電源をドライバ電源電圧に使用した場合と同程度の特性が得られた。

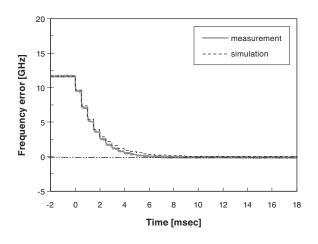

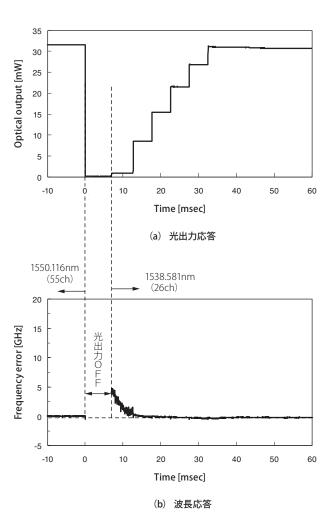

図9に、波長可変レーザ制御ICを用いて当社製波長可変レーザを制御した際の波長応答の測定結果を示す。これは、波長制御を停止した状態で発振波長が目標値からずれた値になるようにレーザ電流を設定し、T=0秒の時点から波長制御を開始した際の応答である。目標波長から約12GHzずれた波長からでも5ミリ秒程度で目標波長に収束しており、周波数誤差は目標値の+/-1.5GHz以下に対して非常に小さく安定した波長制御ができている。

図10は、波長可変レーザの発振波長を1550.116nm (55ch)の設定波長において安定動作している状態から、1538.581nm (26ch)の波長に設定を切り替えた時の光出力および発振波長の時間変化を示した結果である。この測定では、波長可変レーザが安定動作している状態から光出力を瞬時に遮断し、次の設定波長に対するパラメータを各部に設定したうえで光出力を所望の値まで上昇させてい

図9 波長応答

図10 波長切替時の応答

る。光出力強度、発振波長とも50ミリ秒以内の短時間の間に目標値まで収束できている。今回、波長切替の測定結果の一例を紹介したが、波長切替に対する光出力の変化率や継続時間についてはステートマシンの設定で調整可能で

あり、要望に応じて波長切替のタイミングを変更することが可能である。

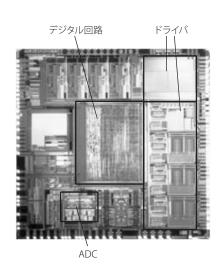

写真1に開発した波長可変レーザ制御ICの外形を示す。本ICは $0.18\mu m$ の CMOS プロセスにて作成し、ICチップの外形は $5mm \times 5mm$  である。最後に、 $\mathbf{表2}$ に本波長可変レーザ制御ICの概略仕様を示す。

写真1 ICチップ写真

#### 表2 波長可変レーザ制御ICの概略仕様

| 電源電圧              | + 3.3V +/- 7 % |

|-------------------|----------------|

| チップサイズ            | 5mm × 5mm      |

| パッケージサイズ          | 7mm × 7mm      |

| パッケージ             | 56pin-QFN      |

| ゲート数              | 880k ゲート       |

| 消費電流<br>(ドライバを除く) | 49 mA          |

## 5. 結 言

小型波長可変光源用途に波長可変レーザ制御ICを開発した。当社製波長可変レーザと組み合わせて特性評価を行ない、低消費電力を実現するとともに光出力、発振波長に対しても良好な特性を示すことを確認した。本ICは、micro-ITLAなどのデジタルコヒーレント光通信システムのプラガブルトランシーバに搭載する小型波長可変光源に適用可能である。

#### 用語集-

#### ※1 周波数誤差

光の発振波長と発振周波数には以下の関係がある。 発振周波数 [Hz] =光速 [m/s] /発振波長 [m] 1.5GHzの周波数誤差は、約12pmの波長誤差に相当する。

#### ※2 バックコンバータ

降圧コンバータ。入力されるパルス信号に対し、その デューティ比に比例した電圧を高効率に出力する回路。

#### ※3 ステートマシン

制御信号を作り出すための順序制御回路。入力条件と現在の状態によって次の状態が決まる。

####

- (1) OIF-ITLA-MSA-01.2, "Integrable Tunable Laser Assembly MSA"

- (2) OIF-MicroITLA-01.0, "Micro Integrable Tunable Laser Assembly Implementation Agreement"

- (3) 金子俊光 他、「波長可変レーザCSG-DR-LDの単一温度動作構造検討」、2011年電子情報通信学会エレクトロソサイエティ大会講演論文集、C-4-9、pp224

#### 執 筆 者一

**五十川知子\***: 伝送デバイス研究所

田中 啓二 : 伝送デバイス研究所 グループ長

**坂野 英一** : 伝送デバイス研究所

金子 俊光 : 伝送デバイス研究所

上坂 勝己 : 伝送デバイス研究所 グループ長

\*主執筆者