プレスリリース

高品質SiCエピタキシャル基板 「EpiEra®」を量産開始

2017年9月14日

住友電気工業株式会社

当社は、エピタキシャル層に含まれる欠陥を極限まで低減したSiCパワーデバイス用エピタキシャル基板 「EpiEra®」の生産・販売を開始しました。

パワーデバイスは電力制御を目的とした半導体デバイスで、電力、鉄道、自動車、家電などの様々な分野で使われており、近年は、より高効率でエネルギーロスの少ないパワーデバイスが求められています。

その中でもSiC(炭化ケイ素)は、パワーデバイスの低損失・高効率・小型化を可能にする点で最も注目されている材料のひとつです。当社はSiCパワーデバイスの基盤材料であり、その性能・信頼性に大きく影響を与えるSiCエピタキシャル基板の開発を進めてきました。

このたび当社は、長年培ってきた化合物半導体の技術に加え、高精度シミュレーションなどを取り入れた当社独自技術の 「MPZ®*1」 を活用し、4インチ(100mm径)及び6インチ(150mm径)の高品質SiCエピタキシャル基板「EpiEra®」の製品化に成功し、量産を開始しました。

「EpiEra®」は表面欠陥*2や基底面転位*3が存在しない領域の面積率(DFA率*4)において、業界最高レベルの99%以上を達成しています。これにより、 SiCパワーデバイスのさらなる品質の向上と安定化が見込まれます。

本製品は、2017年9月17日(日)~22日(金)に米国・ワシントンD.C.で開催されるSiC及び関連材料に関する国際会議「ICSCRM 2017」の併設展示会に出展予定です。

当社は、今後も高効率でエネルギーロスの少ないパワーデバイス製品の開発を進め、パワーエレクトロニクス産業の発展に貢献してまいります。

-

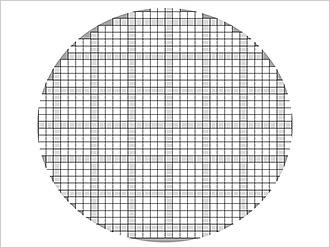

SiCエピタキシャル基板

-

4インチ「EpiEra®」基底面転位マップの例 DFA率 100%

*1 MPZ:

Multi-Parameter and Zone controlled SiC Growth Technologyの略。

SiC成長過程に応じてシミュレーションも活用し、温度や圧力などの種々のパラメータを高精度に制御する当社独自のSiC成長技術。

*2 表面欠陥:

エピタキシャル層の表面に現れる結晶欠陥で、デバイスの歩留りに影響を与える。

*3 基底面転位:

SiC単結晶の基底面に発生する転位で、製品の信頼性に影響を与える。

*4 DFA率:

表面欠陥や基底面転位が存在しない領域(Defect Free Area)の面積率。

以上